# **Solutions - Midterm Exam**

(October 16th @ 5:30 pm)

Presentation and clarity are very important! Show your procedure!

## PROBLEM 1 (20 PTS)

a) Complete the following table. The decimal numbers are unsigned: (5 pts.)

| Decimal | BCD          | Binary   | Reflective Gray Code |

|---------|--------------|----------|----------------------|

| 33      | 00110011     | 100001   | 110001               |

| 57      | 01010111     | 111001   | 100101               |

| 133     | 000100110011 | 10000101 | 11000111             |

b) Complete the following table. The decimal numbers are signed. Use the fewest number of bits in each case: (12 pts.)

| REPRESENTATION |                    |                |                |  |  |  |  |

|----------------|--------------------|----------------|----------------|--|--|--|--|

| Decimal        | Sign-and-magnitude | 1's complement | 2's complement |  |  |  |  |

| -26            | 111010             | 100101         | 100110         |  |  |  |  |

| -64            | <b>1</b> 1000000   | 10111111       | 1000000        |  |  |  |  |

| 23             | 010111             | 010111         | 010111         |  |  |  |  |

| -33            | 1100001            | 1011110        | 1011111        |  |  |  |  |

| -4             | 1100               | 1011           | 100            |  |  |  |  |

| -9             | 11001              | 10110          | 10111          |  |  |  |  |

c) Convert the following decimal numbers to their 2's complement representations. (3 pts)

```

-21.375 \checkmark 19.125 \cdot 21.375 = 010101.011 \Rightarrow -21.375 = 101010.101 \cdot +19.125 = 010011.001

```

## **PROBLEM 2 (16 PTS)**

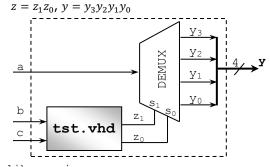

Complete the timing diagram of the following circuit. The VHDL code (tst.vhd) corresponds to the shaded circuit.

library ieee;

use ieee.std\_logic\_1164.all;

```

entity tst is

port (b,c : in std_logic;

z: out std_logic_vector(1 downto 0));

end tst;

```

architecture bhv of tst is

begin

process (b, c)

begin

z <= b & c;

if c = '1' then

z <= b&'1';

end if;

end process;

end bhv;</pre>

• Get the Boolean equations for  $y_3, y_2, y_1, y_0$  based on a, b, c (4 pts)

$$z_1 = b, z_0 = c$$

$$y_3(a, b, c) = z_1 z_0. a = bca$$

$$y_1(a, b, c) = \overline{z_1} z_0. a = \overline{b} ca$$

$$y_2(a,b,c)=z_1\overline{z_0}.\,a=b\bar{c}a$$

$$y_0(a,b,c)=\overline{z_1}\overline{z_0}.\,a=\overline{b}\overline{c}a$$

## **PROBLEM 3 (10 PTS)**

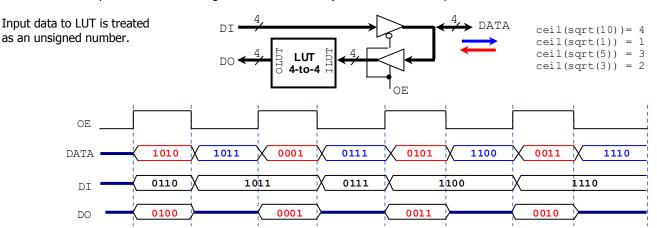

• Given the following circuit, complete the timing diagram (signals DO and DATA). The LUT 4-to-4 implements the following function: OLUT = [sqrt(ILUT)]. For example:  $ILUT = 1100 \rightarrow OLUT = 0100$

#### PROBLEM 4 (11 PTS)

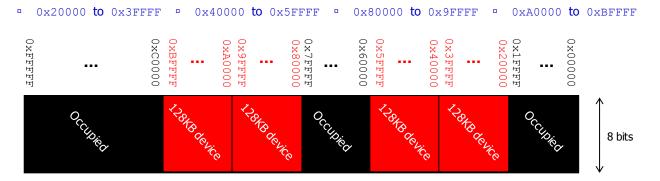

- The figure below depicts the entire memory space of a microprocessor. Each memory address occupies one byte. 1KB = 2<sup>10</sup> bytes, 1MB = 2<sup>20</sup> bytes, 1GB = 2<sup>30</sup> bytes

- ✓ What is the size (in bytes, KB, or MB) of the memory space? What is the address bus size of the microprocessor? (2 pts.)

Address space:  $0 \times 000000$  to  $0 \times FFFFFF$ . To represent all these addresses, we require 20 bits. So, the address bus size of the microprocessor is 20 bits. The size of the memory space is then  $2^{20} = 1$  MB.

✓ If we have a memory chip of 128 KB, how many bits do we require to address those 128 KB of memory? (1 pt.)

128 KB memory device:  $128KB = 2^{17}$  bytes. Thus, we require 17 bits to address the memory device.

✓ We want to connect the 128 KB memory chip to the microprocessor. For optimal implementation, we must place those 128 KB in an address range where every address shares some MSBs. Provide a list of all the possible address ranges that the 128 KB memory chip can occupy. You can only use the non-occupied portions of the memory space as shown below.

#### PROBLEM 5 (17 PTS)

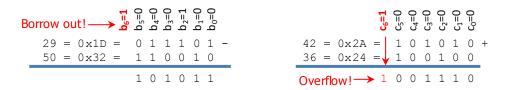

a) Perform the following additions and subtractions of the following unsigned integers. Use the fewest number of bits n to represent both operators. Indicate every carry (or borrow) from  $c_0$  to  $c_n$  (or  $b_0$  to  $b_n$ ). For the addition, determine whether there is an overflow. For the subtraction, determine whether we need to keep borrowing from a higher byte. (6 pts)

b) Perform the following operations, where numbers are represented in 2's complement. Indicate every carry from  $c_0$  to  $c_n$ . For each case, use the fewest number of bits to represent the summands and the result so that overflow is avoided. (8 pts)

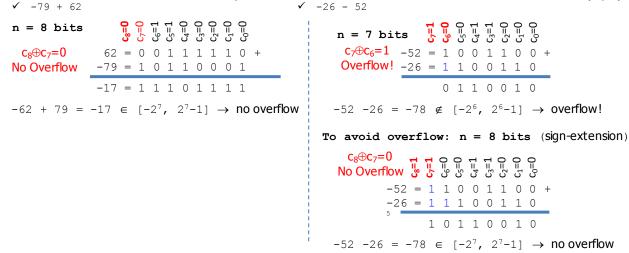

c) Perform binary multiplication of the following numbers that are represented in 2's complement arithmetic. (3 pts) ✓ 7 x -8

#### Problem 6 (10 pts)

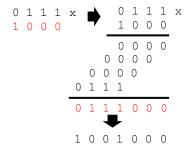

Sketch the circuit that computes  $|A - B| \times 2$ , where A, B are 4-bit <u>unsigned</u> numbers. For example: A = 0101,  $B = 1101 \rightarrow 0.00$  $|A - B| \times 2 = 8 \times 2 = 16$ . You can only use full adders and logic gates. Your circuit must avoid overflow.

$A = a_3 a_2 a_1 a_0$ ,  $B = b_3 b_2 b_1 b_0$

$A, B \in [0.15] \to A, B$  require 4 bits in unsigned representation. However, to get the proper result of A - B, we need to use the 2C representation, where A.B require 5 bits in 2C.

- $\checkmark$   $X = A B \in [-15,15]$  requires 5 bits in 2C. Thus, we need to zero-extend A and B to convert them to 2C representation.

- $\checkmark$   $|X| = |A B| \in [0.15]$  requires 5 bits in 2C. Thus, the second operation  $0 \pm X$  only requires 5 bits.

- □ If  $x_4 = 1 \rightarrow X < 0 \rightarrow \text{we do } 0 X$ .

- $\text{If } x_4 = 0 \rightarrow X \ge 0 \rightarrow \text{we do } 0 + X.$

- $\checkmark$   $R = |A B| \times 2 \in [0,30]$  requires 6 bits in 2C. Note that the MSB is always 0. The unsigned result only requires 5 bits.

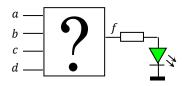

# **PROBLEM 7 (16 PTS)**

- An LED is lit (f = 1) when the combination of four active-high switches (a, b, c, d) represents an unsigned integer that is odd and prime, otherwise f = 0. For example: if  $abcd = 0001 \rightarrow f = 0$ . If  $abcd = 1011 \rightarrow f = 1$ .

- a) Provide the simplified expression for f and sketch this circuit using logic gates. (4 pts)

| a | b | С | d | f |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 |

|   |   |   |   |   |

| $f_{ab}$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 00       | 0  | 0  | 0  | 0  |

| 01       | 0  | 1  | 1  | 0  |

| 11       |    | 1  | 0  | 1  |

| 10       | 0  | 0  | 0  | 0  |

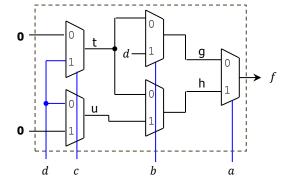

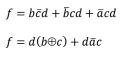

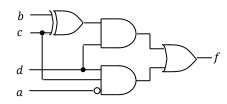

b) Implement the previous circuit using ONLY 2-to-1 MUXs (AND, OR, NOT, XOR gates are not allowed). (12 pts)

$$f(a,b,c,d) = d(b \oplus c) + d\bar{a}c$$

$$f = \bar{a}f(0, b, c, d) + af(1, b, c, d) = \bar{a}(d(b \oplus c) + dc) + a(d(b \oplus c)) = \bar{a}g(b, c, d) + ah(b, c, d)$$

$$g(b,c,d) = \overline{b}(dc) + b(dc + d\overline{c}) = \overline{b}(dc) + b(d)$$

$$h(b,c,d) = \overline{b}(dc) + b(d\overline{c})$$

$$t(c,d) = dc = \overline{c}(0) + c(d)$$

$$u(c,d) = d\overline{c} = \overline{c}(d) + c(0)$$